- 收藏

- 加入书签

NE555芯片:数字逻辑电路芯片测试

摘要:芯片测试是保证产品优良率的重要环节,芯片测试的主要目的是保证芯片在恶劣环境下能够完全实现其在设计规格书中所规定的功能和性能指标,以此来判断芯片的质量是否符合标准,并且是否能够流入市场。本文以NE555芯片为例介绍芯片的测试流程。测试流程中用到的测试电路已在Proteus仿真电路中验证。

关键词:NE555;芯片测试;数字逻辑芯片

Abstract:The test of a chip is an important link to ensure the excellent rate of a product and the corresponding cost and raw material control. The main purpose of chip test is to ensure that the chip can fully realize and ensure the corresponding function and corresponding performance index specified in the design specification in the harsh environment,so as to judge whether the performance of the chip meets the standard. And whether they can enter the market. In this paper,a simple chip test -NE555 chip,to understand the characteristics of 74 series chip test flow. The circuit has been verified in the simulation circuit in Proteus.

Keywords:NE555;74 series;Chip test;Digital logic chip

1 引言

当今电子产品无处不在,其核心是芯片。一枚芯片的生产,包括设计、制造、测试三个环节,其中测试环节是保证芯片能正常使用的关键环节。芯片的测试包括性能测试和功能测试,性能测试主要测试芯片的电气参数,功能测试则是对不同功能的集成电路进行定制化测试。

芯片测试不仅可以用于芯片生产的功能检测环节,也可以用于教学,帮助学生认识和理解逻辑电路。

本文试图以一个简单的芯片测试电路入手,将测试芯片的过程展示出来,让学生更好地了解逻辑电路。

NE555芯片是一种相当常见的定时IC芯片,其使用面非常广泛,并且只要少量的电容和少量的电阻,就可发出不同的频率脉波讯号。

NE555芯片主要特点:

1.芯片的输出端口提供的电流较大,可直接驱动多种需要自动控制的负载。

2.温度稳定度佳,计时精确度高,并且价格实惠。

3.操作的电源范围大,可与不同的逻辑电路进行配合。

4.需要较少的电容与电阻,就可以实现震荡延时功能。

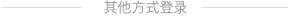

引脚功能:

PIN1:接地线。

PIN2:触发点。触发的范围:上升沿电压大于2/3电源电压,下降沿电压必须低于1/3 的电源电压。

PIN3:此引脚处于高电平时,最大的输出电流大致为200mA。

Pin4:此引脚通常被接到电源或者不用,属于重置的引脚,当引脚输入低电平时,系统会重置定时器,并且使对应的输出回到低电平。

Pin5:当计时器处于稳定状态时,可以调整或者改变输出的频率,此引脚可以由外部电压来改变触发电压。

Pin6:该引脚的输入从小于1/3 的电源电压增加到大于2/3的电源电压时就会开始重置锁定,并且输出低电平。

Pin7:当PIN3的输出为低电平的时,PIN7相对于GND为低电平,当PIN3为高电平时,PIN7对地为高阻态。

Pin8:NE555芯片的电源端。电压的范围从+4.5V到+16.5V。

NE555时基电路通常有两种封装形式,一种是sop-8小型(smd)封装形式,另一种是dip双列直插8脚封装。

采用DIP8,SOP-8封装形式的主要特点有:

1.最大的工作频率可以超过500KHZ。

2.可工作在振荡或者单稳态模式。

3.关闭时间短,通常小于2S。

4.占空比可控。

5.可与TTL电路相接。

6.温度稳定性好。

7.定时精准,通过外接电阻和电容进行精确控制。

8.输出电流较大,可以达到200毫安。

2 NE555芯片

2.1 多谐振荡器

多谐振荡器是产生非正弦周期性波形的电路。该电路可连续或周期性地生成相应的矩形脉冲,且无需增加额外的触发信号。矩形脉冲由基波和多次谐波组成,因此称为多谐振荡器电路。多谐振荡器的应用非常广泛,例如,开车时需要转向灯不停地闪烁,就可以通过多谐振荡器来实现。

非正弦波形有方波、矩形波、梯形波、三角波、锯齿波等。

NE555通过外接电阻和电容输出占空比、频率可调的方波,再通过积分电路实现三角波的输出,还可通过低通滤波器对三角波进行滤波得到正弦波。

积分产生三角波:

1.因为积分器电路中的输出电压会受到工作电源电压限制,所以输出的电压不会无限高,因此需要对积分器的RC参数进行限制,即保证RC不能太小,否则将会导致产生的三角波被削顶,最终成为“平顶波”。

2.输入方波的频率和幅值,也会影响输出三角波的最大峰值限制。

3.其它条件不变,输入方波幅值越高,三角波的输出幅值越高。

4.其它条件不变,输入方波频率越低,三角波的输出幅值越高。

电阻R1、R2和电容C1组成NE555的基本电路。

多谐振荡器的放电时间常数分别为:

tPH≈0.693×(R1+R2)×C1

tPL≈0.693×R2×C1

振荡周期T和振荡频率f分别为

T=tPH+tPL≈0.693×(R1+2R2)×C1

f=1/T≈1/[0.693×(R1+2R2)×C1]

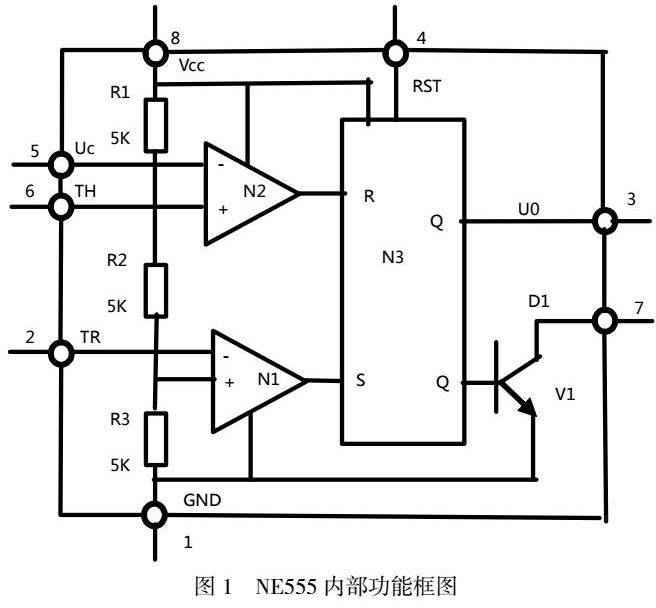

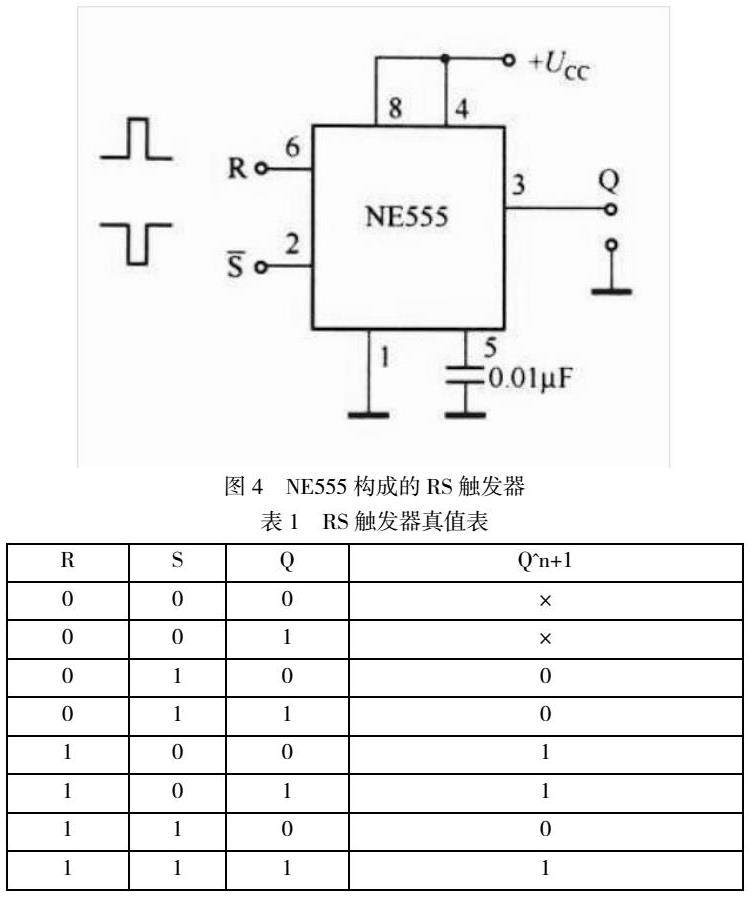

2.2 RS触发器

一般来说,两个与非门或者异或非门可以组成一个基本的RS触发器。RS触发器中的 R 表示 Reset(复位),S 表示 Set(置位)。

要使操作按照一定的顺序执行,单独使用组合逻辑电路是无法实现的,还需多种组合逻辑电路串联起来,如果这些电路通过硬件来实现代价是非常大的,而且其灵活性也得不到保证。因此可以构建一个可以在操作之间存储信息的电路,以实现高效灵活的操作顺序。这样的电路称为时序电路。

数字电路中时序逻辑电路的故障分析方向:

1.复位:任何一个包含微处理器的设备,哪怕是最小系统,一般都包含有复位功能。当系统接通电源时,复位脉冲传输至微处理器上,或者在某种情况下能够使程序返回至原始状态。

2.时钟:整个系统的同步信号就是时钟。系统时钟故障时,整个系统就会出现故障。丢失时钟脉冲将造成系统数据总线、控制总线或地址总线不工作的情况。其中,时钟脉冲的幅度、宽度、速度、相位以及形状的变化都有可能出现异常。

3.总线:一般有控制总线、数据总线和地址总线。如果总线出现任何异常,都会对系统的正常运行造成严重影响,包括错误操作、错误数据、或错误寻址等。其他接收数据位的组件或总线的驱动器中也可能发生总线异常。

4.信号畸变和衰减:交互式串扰和传输线故障可能是由并行总线或长控制线导致的,其表现为相邻信号线的峰值脉冲,也就是驱动线的阻尼振荡,或交互式串扰,出现错误控制信号或数据增加的情况。信号衰减的原因较多,例如高湿度环境、转换速率高、传输线长等,还有EMI、较大的电子干扰源产生的电磁干扰,从而会造成信号失真以及电路的功能紊乱。

5.中断:具有微处理器的系统通常能够响应中断信号或设备请求、提供中断服务、中断响应后再回到主程序中。中断错误主要是由于中断线路粘附,即操作系统变得非常慢,或接收到干扰,即系统错误地响应中断请求造成的。

检测时序逻辑电路的步骤:首先熟悉系统结构以及原理,然后分析电路故障特征,从而缩小故障范围。

6.检测电源:时序逻辑电路使用的供电电源在+5V到+15V之间。当电源短路或者稳定性较差时,系统出现故障的概率极大,主要表现为系统无响应、程序无序等。很多情况下,电源短路是由于电容故障,一般是因去耦电容短路导致的,确定短路电容最好的方法是使用电流跟踪器,它可以追踪短路的电流。

7.检测时钟:大部分电路是由石英晶体电路来组成的。然而石英晶体容易损坏。检测时钟信号的频率,幅度以及相位可使用示波器,或者通过逻辑探头检测时钟脉冲的存在与否。检测时应注意每个单元电路的时钟,防止因断线、松动和干扰而造成错误时钟脉冲。

8.检测总线:如果系统没有脉冲信号,可通过使用逻辑探头检查总线的脉冲活动,查看驱动器的状态,最终确定故障是否由总线驱动器引起的,如果没有故障,再依次检查各个总线的接收器。此外,还可以使用万用表关闭电源并检查总线的每条线路的接地电阻。如果所有线路的电阻值相同,则说明总线是正常的;如果其中一条或者多条的电阻值不相同,那么说明此总线是损坏的。

当引脚6(即R端)的电压高于(2/3)VCC时,输出为低电平。当引脚2(即S端)电压低于(1/3)VCC时,输出为高电平。

当R=S=0时结果不能确定,所以为拒绝使用的状态。

当R=0,S=1时,Q被置0。

当R=1,S=0时,Q被置0。

当R=S=1时,Q保持不变。

3 总结

随着科技的进步,时代的发展,芯片的需求量将越来越大,研究一套芯片测试的方法是非常有意义的,该方法能够测试出芯片质量并判断其性能是否优良,这可以极大减轻生产企业的成本、研发工程师的工作量。在恶劣环境下测试芯片能否实现设计规格书中所规定的功能并达到其性能指标,即可决定芯片是否可以流入市场。

参考文献:

[1]一种基于555时基电路的振荡器设计[J]. 张璐雅;阮景.集成电路应用,2019(12)

[2]一种基于NE555定时器的气敏报警器的设计[J]. 高志东;白泽生.电子设计工程,2017(02)

[3]基于NE555方波脉冲发生器的设计及应用[J]. 文华兵;陈常婷;刘频.现代电子技术,2014(11)

[3]基于NE555设计的脉冲信号发生器在实践教学的应用[J]. 苏文平;薛永毅.实验技术与管理,2008(06)

[4]与非门抢答器的制作[J]. 吴建宁.电子制作,2005(06)

[5]基于RS触发器的四人抢答器电路仿真设计[J]. 金灵.电脑知识与技术,2019(19)

[6]CMOS集成电路课程教学的探讨与实践[J]. 贺旭;邓全利.计算机教育,2019(06)

[7]高速数字电路设计研究[J]. 周堃.航空计算技术,2003(02)

[8]数字电路设计方案的比较与选择[J]. 鲁欣,赵亦工,徐秀红.电子技术应用,2002(01)

[9]数字电路设计中应考虑的因素与抗干扰问题研究[J]. 王会云.技术与市场,2017(12)

[10]基于74系列八路抢答器的设计[J]. 李丽红.科技信息,2009(35)

(作者单位:成都职业技术学院)

< a rel="example_group" title="Custom title" href="http://img.resource.qikan.cn/qkimages/a57b/a57b202321/a57b20232101-3-l.jpg">

< a rel="example_group" title="Custom title" href="http://img.resource.qikan.cn/qkimages/a57b/a57b202321/a57b20232101-3-l.jpg">

京公网安备 11011302003690号

京公网安备 11011302003690号