- 收藏

- 加入书签

基于PUF技术的安全打印耗材SOC芯片设计

一、摘要

1.国内外技术发展现状及趋势

安全芯片硬件相关理论与技术一直是当前学术界和工业界关注的重要研究领域之一,国内外很多大学和科研机构均在这一领域进行了深入广泛的研究,并取得了一些有代表性的研究成果。物理攻击是最早出现的硬件攻击技术。攻击者通过打开芯片封装,使用光学图像实施逆向工程进行版图重建,从而直接复制芯片或直接读取掩膜 ROM 中存储的关键信息内容;也可以在不破坏芯片的情况下通过微探针工作站探测芯片总线上的信号;或者使用聚焦离子束(Focused Ion Beam,FIB)或电子束测试仪(Electron Beam Tester, EBT),直接从外部探测芯片内部信号。或者通过异常温度电压者紫外线技术改变芯片内EEPROM存储的关键信息从而破解芯片。物理攻击的目的,是通过各种技术手段在芯片工作或非工作状态下直接探测芯片内非易失性存储器、寄存器或者总线上传输的信号,从而获取加密密钥、用户ID、关键配置等信息,往往是一种侵入式和破坏性的攻击。

物理不可克隆(PUF)技术的出现,为低成本抗物理攻击防护技术提供了一种新的解决途径。世界主要的智能卡芯片生产厂商之一恩智浦(NXP)在其新一代SmartMX2智能卡中采用了Intrinsic-ID公司的PUF解决方案来增强安全性。Altera公司也在其Stratix® 10系列高端FPGA中采用Intrinsic-ID公司的PUF技术来防止篡改和克隆攻击。

PUF最早由Pappu等人提出,早期称为物理单向方程(Physical one-way functions),后来才统一称为物理不可克隆方程。PUF可以看做是芯片的“物理指纹”,它是唯一且不可克隆的。目前已提出的PUF电路实现结构主要包括基于判决器的PUF电路、基于环路振荡器(Ring oscillators, RO)的PUF电路,基于SRAM单元的PUF电路和基于Latch单元的PUF电路等。这些实现电路主要通过采样电路单元中的特定物理特性的变化,然后经过比较和放大之后产生数字响应。然而,现有PUF存在的一个主要问题是无法抵抗侵入式攻击,在PUF工作状态下(Power-on),攻击者仍然可能通过非破坏性探针直接探测信号线或者存储器上的数据从而破解PUF的密钥。

综合以上情况,国外研究机构虽然在安全芯片硬件安全领域取得一些代表性研究成果,但仍然存在一系列的科学技术问题亟待解决。而在国内,由于起步较晚,与国外先进技术相比还存在较大差距。因此,本课题希望能够在消化吸收现有研究成的基础上,自主创新,提出新型的高效低成本防护实现技术,形成自主的高效能安全芯片硬件安全防护技术理论与实现技术体系。

2.国内外市场需求分析

2013年全球打印机市场销量为八千万台左右,2014年上半年的销售量又有0.2%的小幅增长。但整体而言,近来全球打印机市场呈现稳中有升的发展超势。随着全球整体经济的逐渐复苏和打印机普及程度的提高,用户对打印耗材的需求也将有所增长。预计未来五年全球打印耗材市场的出货金额将基本保持增长,但市场的日渐成熟将使整体增速保持平缓,难以出现快速增长的局面,预计未来五年内年均复合增长在0.3%左右,2018年将达到七百多亿美元。

中国打印机市场的逆势增长很大程度上带动了打印耗材市场的快速发展,但中国打印耗材出口比例较高,中国打印耗材出货金额趋于稳定。近年来,除2012年受欧州危机加剧不利影响导致中国打印耗材市场出货金额同比有所下降外,其余年份基本都呈现增长趋势。其中,2013年出货金额为1242.74亿元,同比增长了1.2%,2014年上半年则达到609.90亿元,同比增长2.1%。总体来说,中国打印耗材的出货金额五年都保持了1200亿元以上的规模,预计未来五年中国打印耗材出货金额的年均复合增长为2.7%左右,2018年达到1421.41亿元。

三、设计实施

1.主要实施内容

本芯片使用了基于32位ARM核的SOC设计平台,采用软、硬件协同设计技术,基于PUF IP的身份认证技术对数据加解密技术等进行设计和开发、內置通用加密引擎模块。可根据实际应用对数据进行高强度加密,并几乎无法破解。本项目的PUF(物理不可克隆)技术填补了国内市场在抗物理攻击防护的空白,属于国内领先水平。本芯片的物理安全设计,以及通用型的SOC架构,兼容主流的ARM开发平台,系统应用上可以实现快速的移植。在嵌入式安全以及物联网应用等方面,提供安全的保护之外,低功耗,多种应用协议,以及灵活的硬件算法加速模块,可以快速定义用户自己的加密算法,同时保证了加密算法的安全有效,也可以为用户提供定制化的安全保护。

1.1、适应通用安全芯片需求的防物理攻击SOC平台设计(抗物理攻击的通用安全芯片SOC平台设计)

现有的安全芯片硬件安全防护体系架构主要面向各种攻击技术,通过将各种攻击的防护技术有效集成构成整体防护系统。但随着物理攻击技术的出现,防护体系变得庞大而复杂,实现成本过高。我司在研究了市面上主流的安全芯片的基础上,构建高效的安全芯片硬件防护体系结构,并利用软硬件结合,搭建基于ARM CPU的SOC平台,完成整体架构设计。

1.2、基于PUF的抗物理攻击防护单元设计

物理不可克隆函数(Physical Unclonable Functions,PUF)电路是一种依赖芯片特征的硬件函数实现电路,具有唯一性和随机性两项独立的特征,通过对芯片制造过程中必然引入的工艺参数偏差,实现激励信号与响应信号唯一对应的函数功能。与传统密码学的密钥提取方案不同,PUF采用激励-响应对(Challenge Response Pairs,CRPs)的方法提取密钥,激励响应对之间的映射关系仅由设备个体的某些物理偏差决定,而这些物理偏差是生产制造过程中无法被人为控制或复制的细微差异决定的。即便知道了原电路的详细设计,也不能制造出完全一致的电路。这样,PUF利用电路内在的物理构造差异来对其进行唯一性标识,输入任意激励都会输出一个唯一且不可预测的响应。

利用PUF来构建抗物理防护体系是一种安全且经济有效的方式,可靠的PUF实现电路的设计是基础。我司采用格罗方得55nm工艺技术,全定制方式设计出了128bit输出的PUF电路。利用标准工艺库的参数漂移偏差,可提取16bit,32bit,64bit的随机密钥作为芯片的唯一身份ID,并且此ID,每颗芯片具有唯一性,随机性,不可窥探性。

1.3、基于STD LIB的PUF单元物理设计

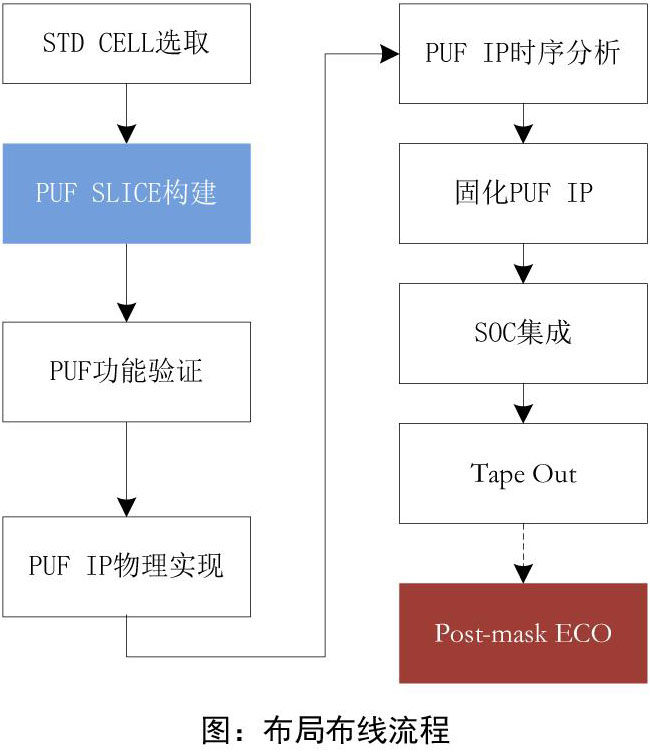

采用基于格罗方得55nm的标准单元库(STD LIB)物理设计流程方法,对PUF的基本单元进行设计,由于没有特殊的器件需要,具有很高的通用性和可移植性。PUF IP设计主要分为以下9大步骤:

1.4、通用加解密引擎模块设计

安全芯片内部集成市面上主流加密引擎模块,包括经典对称密钥算法,比如AES、DES、3DES等,经典非对称密钥算法,比如RSA、ECC等,还包括经典ID认证算法,比如SHA等。这些经过市场多年验证过的加密算法具有极高的算法安全性,可以配合SoC的各种应用场景,基于PUF生成的唯一密钥进行组合加解密,进一步保证了芯片的安全性。

1.5、安全模块设计

芯片内部集成了各种模拟检测模块,包括模拟的电源监测、功耗监测、顶层防篡改监测、内部信号线防篡改检测、光敏检测等等。在芯片检测到外界环境的变化时,会进行相应的自毁操作,让芯片内部的安全数据保证不被窃取。

2.核心技术路线

2.1、安全的硬件防护SOC架构

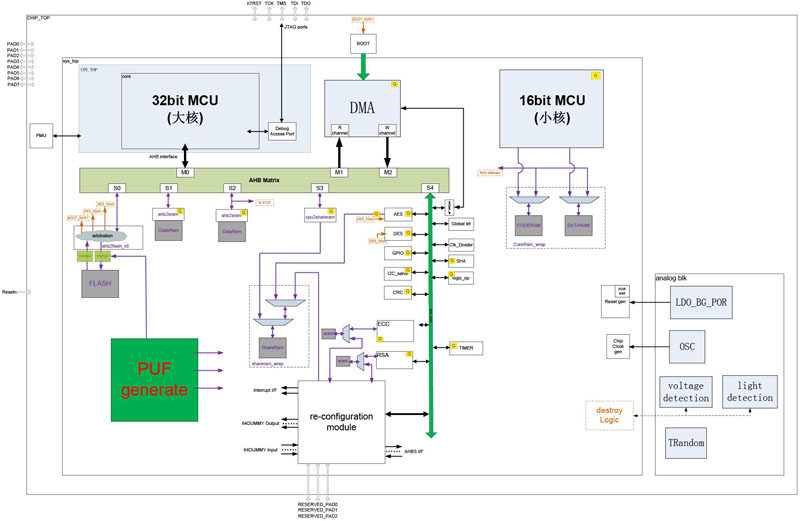

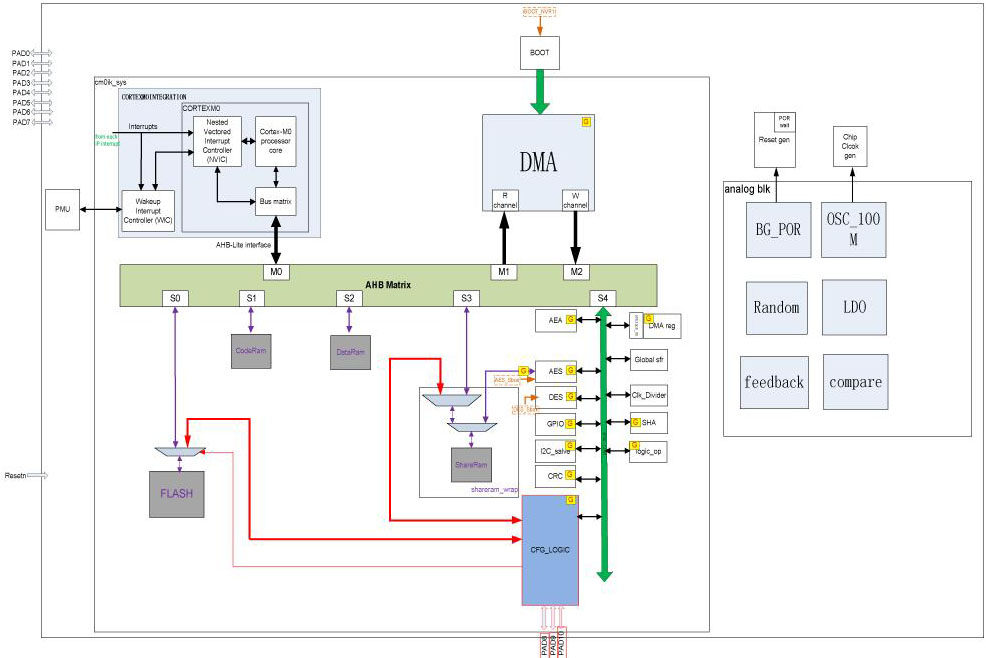

在对安全芯片硬件攻击技术的深入研究与分析基础上,本项目初步构建的安全芯片SOC架构如图所示。

该架构主要包括CPU核、PUF IP产生电路、存储器管理、总线与存储器加密、安全辅助单元、控制保护逻辑、真随机数产生器以及内部时钟、电源管理等模块。其中,CPU内核采用32bit和16bit大小双核设计,用于适应各种不同的应用。PUF电路作为系统根密钥存储单元,在固定指令激励下实时产生唯一的不可复制和探测的响应序列作为根密钥,结合真随机数产生器构建随机动态密钥对总线和存储数据进行加密,同时通过CRC进行完整性校验,保证传输与存储数据的机密性与完整性。

本架构从静态安全和动态安全角度进行了系统性考虑。在芯片不工作的静态状态下,由于存储数据被加密保护,而加密密钥由PUF电路工作时实时产生,非易失性存储器中只存储了PUF的动态口令,所以攻击者无法探测到密钥和数据;侵入式的探测则会破坏PUF电路从而破坏PUF特性,安全芯片将被锁死。(在芯片上电的动态状态下,顶层金属布线层能实时检测到物理探测,当窥探者利用FIB对芯片进行修改时,会破坏顶层的绕线,控制保护逻辑将使芯片进入自毁程序。)该系统架构不需要采用任何传感器,另外,由于PUF和随机数产生器构建的动态密钥具有随机性,即使简单的异或加密操作也能确保数据一定程度上的安全性,可以有效解决采用公开加密算法带来的性能和带宽损失。因此,该体系架构比现有安全芯片防护体系安全性更强,而实现成本与开销更低。

2.2、基于PUF的芯片片内随机源防破解设计

为了保护加密芯片的片内真随机数产生器(TRNG)免遭破坏和探测,本项目拟在处理器内部嵌入一个PUF电路,将PUF电路作为系统根密钥存储单元,在某个固定指令的激励下实时产生唯一的不可复制和探测的响应序列作为根密钥,对TRNG产生的随机数进行加密,以保证随机数的机密性。由于PUF产生的密钥具有不可探测性,即使简单的异或加密操作也能确保数据安全。另外,将PUF电路覆盖在TRNG所处的芯片外部区域,一旦攻击者试图利用探针等物理攻击技术破坏或者探测TRNG,势必改变PUF输出,从而PUF电路失效,芯片将被锁死,关键数据被清除,这样就可以有效防止由于随机数产生器失效而引起的片内重要数据的遗失。

2.3、基于PUF的辅助安全单元设计

主要研究了ST/TI在安全芯片的安全技术,对该领域的系列产品的安全方案进行整合研究,与工艺厂配合开发自主安全的定制单元,以及混淆单元。对于顶层监测以及其他安全监测模块,总线安全,混淆方案采用自主开发技术路线,先进行软硬件的评估,设计。后期利用自己的FA实验室平台评估安全的可行性。

伪装单元设计:

1).GATE底下缺少DIFF,达到器件伪装效果,从而达到IC伪装效果。

2).隐身的掺杂水平的硬件木马,实际恒输出1

FA失效分析区分N注入还是P注入,主要通过金相显微镜结合化学染色来完成的,在55nm的工艺下,金相显微镜的分辨率不足,照片模糊。难以区分N注入以及P注入。在物理剖层来分析器件或者电路逻辑,破解层面已经宣告失败。

N注入和P注入的电子反射能量原理,在通过加入大量的伪装逻辑电路,在55nm以及数字电路规模已经上百万的门的基础上,从大量的伪装期间中寻找实际的正确逻辑一定程度上已经难以做到。

Layout顶层保护设计:

通过Layout在顶层金属进行密集绕线,对下层的逻辑信号和一些关键数据,以及PUF进行保护。当窥探者利用FIB对芯片进行修改时,会破坏顶层的绕线,从而使内部逻辑产生自毁操作。

2.4、真随机数生成模块

从某种意义上来说,随机序列的安全性确定了整个安全体系的安全性,相对于完全采用数学方法生成的伪随机数发生器而言,真随机数发生器取自真实物理世界的随机源,不可重复和破解,具有更高的安全性。

本芯片内置了基于时钟相位抖动的真随机数生成器,用来得到初始密钥种子,以得到非常好的随机和不可预测性。完成该模块的设计和仿真。

4.关键创新点

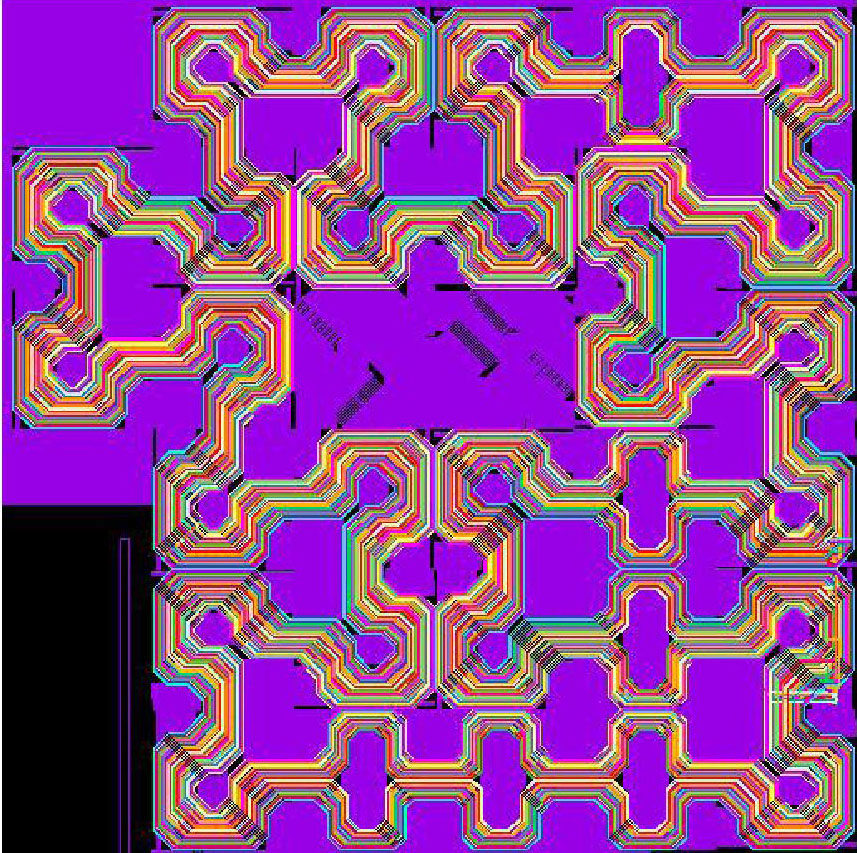

4.1、创新点一:自主研发设计了Layout顶层绕线保护结合PUF的保护电路,该电路能有效防护物理攻击旁路攻击等窃取PUF电路产生密钥的手段,极大提高PUF电路本身的安全性。

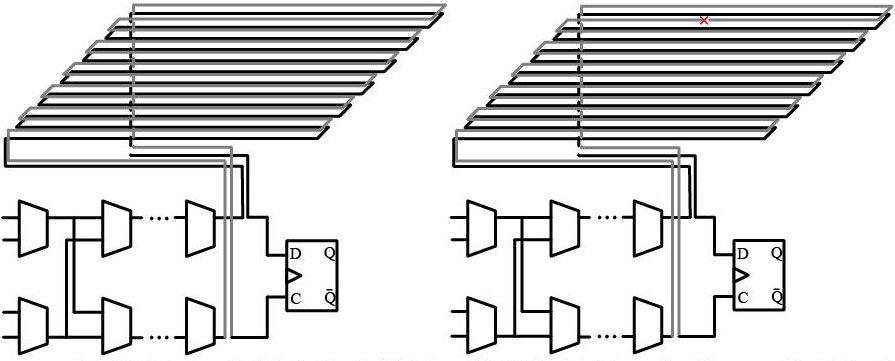

本方案在PUF基本电路的基础上,将PUF输出走线延长,并在版图顶层密集绕线,把所有的数字逻辑单元和存储器单元保护在密集绕线之下,从而达到保护逻辑电路和存储器不被窥探的目的。

本方案的创新在于,顶层绕线保护直接输入PUF单元,一旦窥探者利用外部手段(比如探针,FIB等)改变内部线路结果,必然会破坏顶层金属绕线,势必会改变PUF的密钥输出结果。此时控制单元发出自毁指令使芯片锁死并清除存储器数据,起到保护芯片的作用。

顶层金属绕线版图如下:

4.2、创新点二:设计了在PUF基本电路的基础上,将伪装单元嵌入PUF电路,在给PUF电路输入挑战(challenge)的同时,混入伪装单元的输出值,从而达到混淆电路的目的。

本方案的创新在于,伪装单元本身能够很好的伪装成标准单元,但逻辑行为与标准单元完全不同,能让最大限度的迷惑反向分析者,更深程度的增加PUF的安全性,从而提高芯片自身的安全性。

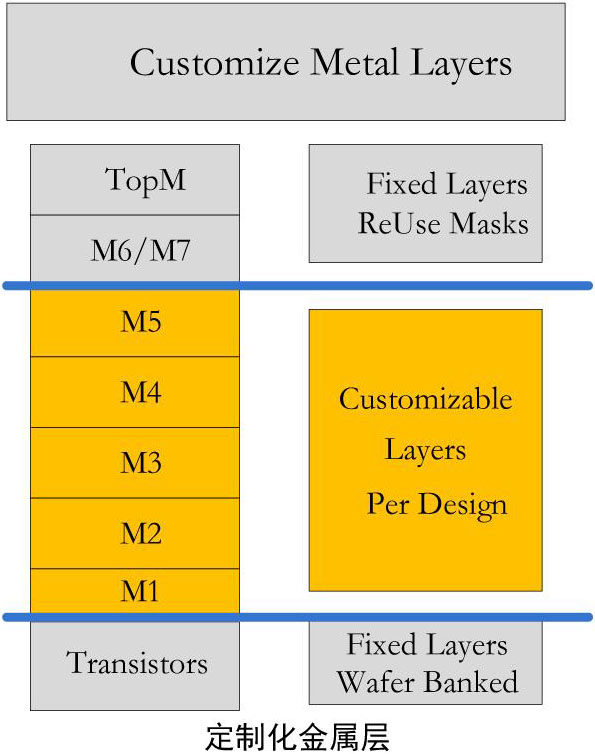

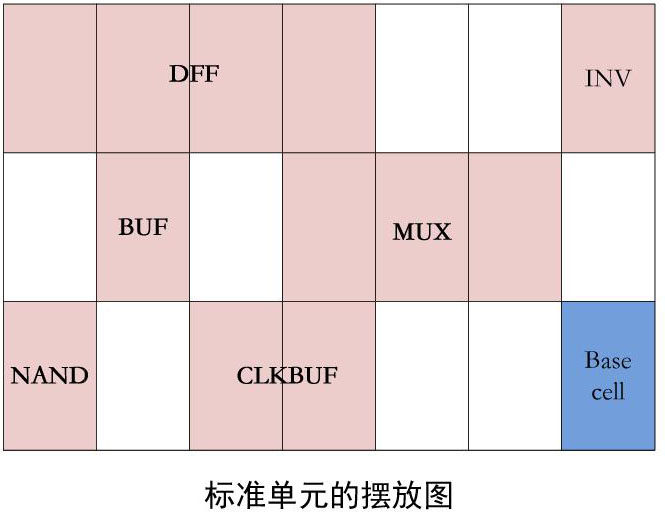

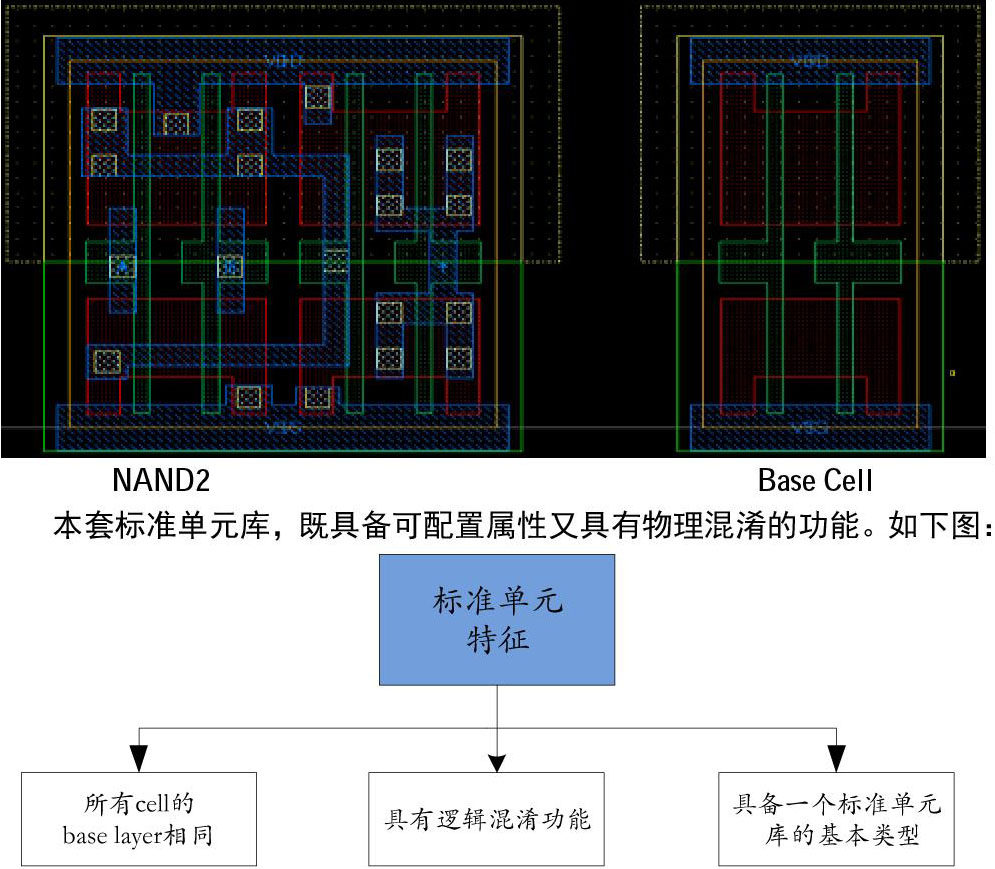

伪装单元为我司自主设计的一套标准单元库-MCLO单元库,其中单元本身以Base Cell为基础展开设计,所有单元的base layer一样,从Contact以上的层次包含Contact、Metal 1、Via1、 Metal2等以上的层次不同。层次描述如下图:

标准单元的摆放图如下:其中,base cell为标准单元库的最基本的单元,4个transistors。

详细版图见下图:

4.3、创新点三:首次将PUF技术引入到耗材安全芯片中,并实际应用于本公司的各型号的耗材芯片,经验证很好有效的防护外部物理攻击,极大提高SOC芯片的安全性。

本项目基于PUF电路设计了SOC芯片安全系统,通过PUF电路本身的唯一性、不可克隆性产生密钥,同时通过Layout顶层绕线保护对PUF电路本身进行保护,使其产生的密钥可以避免窥探者通过物理攻击的手段窃取,同时在PUF电路中嵌入伪装单元,在给PUF电路输入激励的同时,混入伪装单元的输出值,从而达到迷惑窥探者的目的。在芯片不工作的静态状态下,由于存储数据被加密保护,而加密密钥由PUF电路工作时实时产生,非易失性存储器中只存储了PUF的动态口令,所以攻击者无法探测到密钥和数据;侵入式的探测则会破坏PUF电路从而破坏PUF特性,安全芯片将被锁死。在芯片上电的动态状态下,顶层金属布线层能实时检测到物理探测,当窥探者利用FIB对芯片进行修改时,会破坏顶层的绕线,控制保护逻辑将使芯片进入自毁程序。该系统架构不需要采用任何传感器,另外,由于PUF和随机数产生器构建的动态密钥具有随机性,即使简单的异或加密操作也能确保数据一定程度上的安全性,可以有效解决采用公开加密算法带来的性能和带宽损失。因此,该体系架构比现有安全芯片防护体系安全性更强,而实现成本与开销更低。防护机制如下图所示。

4.4、创新点四: 软硬件结合设计,优化设计的可靠性,IP的重复利用,简化设计,提高产品的快速迭代以及质量保证。

MASK成本支出以及模拟IP的可靠性,在IC设计中占据重大的考量因数。经过大量硅验证的IP是IC设计公司的主要财富。可配置的SOC设计,把经过验证的IP的使用发挥到极致。设计人员只需要考虑可配置部分的逻辑的安全性与可靠性。在数字IC设计领域,EDA设计自动化以及流程的成熟与完善,风险大大降低。

如上图所示,红色部分为配置逻辑,包括3个可配置的PAD(可以增加),增强协议方面的通用性以及定制开发通信协议。可配置逻辑使用MCLO设计,兼容现有的RTL到netlist的流程,与内核总线接口采用标准的AHB协议,端口清晰明了。只要空间或者预留的门数足够多,能够适应RTL到netlist的正常设计流程,无需增加。在设计时序上对比FPGA的LUT结构减少冗余单元设计,与正常流程的标准单元设计无差异,在设计面积以及功耗,速度上更接近标准的ASIC设计。对于模拟部分以及arm的内核设计,基础的算法,通用的外设模块采用固定的IP设计,继承了原有IP的正确性以及可靠性,对设计者和开发者都大大减少了工作量,尤其是设计风险。对于ARM核部分能够适应大部分的常规的嵌入式应用,对于其他的特殊需求的应用,往往需要重新立项,设计,流片,验证。不仅仅耗费大量的时间和资金,在风险上也难以控制。本方案设计,只需要修改配置部分的逻辑重新设计和布局布线,大大减少了工作量。软件应用和硬件的定制化设计丰富了产品的应用范围和性能的提升。

5.主要技术成果

5.1、知识产权情况

本项目完成时,已授权2项发明专利、2项实用新型、1项软件著作权、1项集成电路布图设计。

5.2、用户应用情况

(1)、珠海市天硌环保科技有限公司

应用时间: 2020年12月

用户反馈:

我公司于2020年12月引进杭州旗捷科技有限公司的“基于PUF技术的信息安全SOC芯片”,主要用于针对爱普生/惠普/佳能等喷墨和激光打印机系列,芯片采用物理防护和软件加密双层保护机制,对内部敏感数据保护的同时对自身物理版图进行防破解,让芯片无论在存储器内部的数据和通讯端口的数据均无法的攻击者获取,大大提高了芯片的数据安全性。

经过一段时间的使用,该芯片产品可兼容爱普生/惠普/佳能等打印机系列,以低功耗运行,具有可循环使用、抗静电能力高、数据存储时间长、成本低、安全保护等特点。

(2)、珠海联合天润打印耗材有限公司

应用时间:2021年1月

用户反馈:

我公司于2021年1月引进杭州旗捷科技有限公司的“基于PUF技术的信息安全SOC芯片”,主要用于针对爱普生/惠普/佳能等激光打印机系列,采用STD cell的delay工艺偏差,实现PUF安全技术。并采用此技术应用于多款耗材芯片的加密算法的秘钥生成。由于PUF技术的不可克隆的特性,大大提升了芯片的安全性。。

经过一段时间的使用,该芯片产品可兼容惠普/佳能等打印机系列,以低功耗运行,具有可循环使用、抗静电能力高、数据存储时间长、成本低、安全保护等特点。

京公网安备 11011302003690号

京公网安备 11011302003690号