- 收藏

- 加入书签

基于FPGA的多端口网络协议解析加速卡硬件电路的设计研究

摘要:研究针对传统网络空间管理难度大、监管手段单一等问题,设计了基于FPGA的多端口网络协议快速分析,以PCIe Gen3×16、4个通道QSFP28 100Gb/s串行光模块接口作为硬件组成,引入400Gb/s的网络加速卡系统,设计时钟、电源方案,以实现网络协议快速分析。仿真试验结果证实该设计方案可保障高速信号的顺利传输,性能达标。

关键词:FPGA;多端口网络协议;加速卡硬件电路;仿真试验;板卡时钟方案

进入21世纪,互联网信息技术飞速发展,对人们的生活及社会生产产生了极大的影响,随着网络应用范围的扩大以及网络性能的提升,安全网关吞吐量也呈现出成倍增加的趋势,与此同时安全网关也逐渐向UTM、Web访问管理等领域扩展。因此需要有更为强大的CPU处理能力及数据分析能力保障网络的高速运转[1]。目前,网络监控系统多采用分级、分区域化管理方式进行数据接入,数据解析需要投入大量的人力。作为可编程逻辑阵列,FPGA具有集成度高、执行速度快、编程灵活等优势,但处理能力低于ASIC,功耗较ASCI大,基于此研究设计了多端口网络协议解析加速卡,并对其硬件电路具体设计进行探讨,以期为相关领域提供参考。

1基于FPGA的协议解析加速卡及硬件电路设计需求

FPGA是编程技术发展到一定阶段的产物,其拥有丰富的内部逻辑资源,灵活性强,目前FPGA推出了一系列IP core,并将其在芯片内部集成,使得网络处理能力得到了大幅度的提升。网络加速卡应用于FPGA编程则能够实现以往编程系统难以实现的功能,覆盖数据预处理、解压缩以及视频编码等功能;应用于其他领域则能够完成大数据分析与文本搜索、算法验证等[2]。为提升网络数据处理速度,满足市场需求,研究设计了基于FPGA的多端口网络协议解析加速卡(FBC-810x),其包含了4个接口,以太接口4×40G、4×100G,主板与模块间接口为2个PCIe 3.0×8,接口速率为128Gb/s。为实现预期目标、确保系统稳定性,板卡设计了时钟模块、电源变换模块与DRAM存储模块等。电源设计应注意剔除旁路、去耦电路的影响,其次要对信号完整性进行合理化设计,解决期间产生的信号串扰、信号衰减等问题。

2基于FPGA的协议解析加速卡硬件电路设计方案

研究在选择处理器件时,充分考虑了功耗、功能及成本情况,经过综合评估最终选择XCZU19EG FPGA,其包括可编程系统(PS)与可编程逻辑(PL)两个部分,经高级总线协议的互联总线连接,PS部分功能可在PL外部管脚映射,此外其还具有保护加密、系统监视等功能。PL部分有触发器、查找表、系统逻辑单元块等,11个时钟管理单元,能够满足接口数量需求。PL DDR3地址、数据及控制总线与HP 68-71 Bank连接;光模块由HD 88-89 BANK驱动,进而实现I2C通信;PS 500 MIO与NOR FLASH互联,PS MIO用于TF卡、I2C等通信接口[3]。完成上述外设连接后,需要做好时钟电路与供电设计。

2.1板卡时钟方案设计

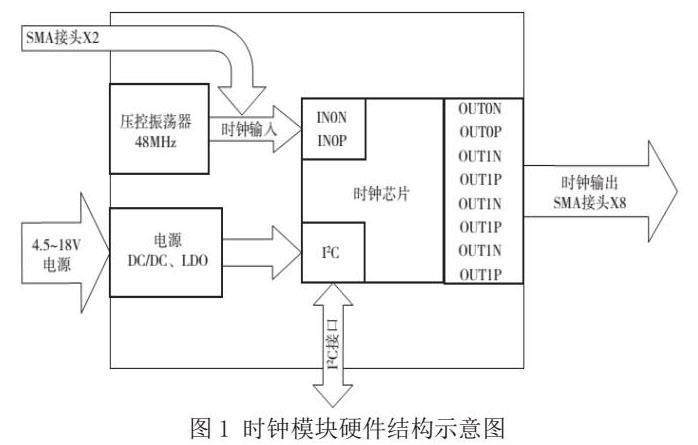

研究针对时钟模块设计了单独的单板,以便为多个芯片提供时钟,其硬件结构如图1所示。时钟模块包含了4个外部接口,对应PS、PL、MGT以及DDR 4部分时钟信号,将Si5340多种输出驱动配置的时钟芯片作为时钟发生器的芯片,配备的有源振荡器为48MHz,独立低抖动,输出频率及驱动配置均能够利用相关软件进行灵活设计。

FPGA PS提供的是主频时钟信号,其不仅负责系统程序的加载,进行芯片上电源单元的管理,而且还具有CPU调试、ARM系统看门狗定时功能。所采用的有源振荡器频率是固定不变的,为50MHz,均方抖动误差在2ps以下,频率稳定,在±10-5范围波动。

FPGA PL部分时钟则是PL提供的主频信号,主要功能为对GPIO信号进行控制,保障芯片逻辑的顺利进行,为外围总线提供参考信号。所用有源振荡器同样为固定频率,但频率较PS部分时钟高,为300MHz,均方抖动误差低,为1ps内[4]。

MGT时钟为高速收发器提供QSFP28、PCIe时钟信号,接口速率提升后,可对时钟提供给Quad的SerDes进行共享与参考,采用该设计方案,每个GTY Bank都拥有独立的参考时钟。

DDR时钟借助芯片Si5340能够为FPGA PS的DDR控制单元提供时钟信号,然后由FPGA向DDR芯片统一提供时钟,在该方案下数据、信息均能够进行有效的交互,有效防止了时序问题的发生。

2.2板卡电源方案

板卡供电通道包括如下两种:(1)配备12V外部电源适配器,插入至4PIN接口完成供电;(2)由PCIe接口中12V电源供电。可引入双电源均流控制器,其集成MOSFET二极管,共享负载能力强。应用该芯片无需对总线、电源的引脚进行共享,便能够实现电源供电或同时供电,可满足供电功率不足状态下的需要[5]。电源芯片来源于3家公司,除为FPGA提供充足电源功率外,还保障了上电顺序的合理性。参照FPGA的用户手册建议,可以设计上电顺序如下:VMGTAVCC、VCCINT、VMGTAVTT。下一个电源EN使能信号主要参照前一电源的PG信号。

3仿真测试

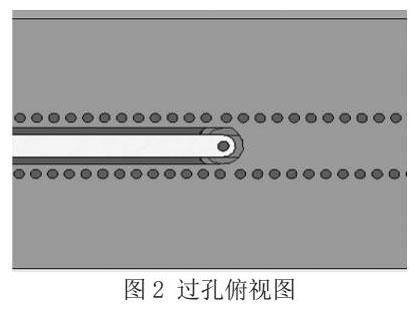

研究针对高速信号线进行了仿真测试,借助Ansys HFSS 3D进行布线,可获得时域反射参数与传输线S参数,根据PCB制板情况判断其效果。研究采用背钻技术以去除过孔未使用的镀层,同时更换顶层传输线至底层,避免出现过孔残桩,导致成本增加。仿真过程中需要先对cadence设计进行格式转换,以ODB++格式导入CST微波工作室,其俯视图如图2所示。CST仿真测试,可以发现5GHz频段过孔阻抗几乎不会导致插入损耗的增加,当>5GHz后,阻抗会导致插入损耗进一步恶化。高速信号过孔换层,经过阻抗优化处理,可以发现插入损耗得到了明显改善。为评估信号传输质量,进行了差分互联,针对其出现的不等长现象,采用蛇形线的方式进行长度调整,可以发现差分阻抗与传输线在0.5mm蛇形线宽下,基本相同;当超过0.58mm后,阻抗较传输线小,能够满足传输损耗的协议规范。

结束语

综上所述,本研究针对FPGA多端口网络协议设计的加速卡硬件电路,时钟硬件方案及电源设计方案完整,配合背钻技术,能够实现性能的优化与改进。仿真测试证实了该设计可对BGA扇出的传输路径、过孔参数等进行优化,性能达标,有一定的应用价值。

参考文献

[1] 丁帅,乔庐峰,陈庆华,等. 多端口TCP协议处理电路的设计与实现[J]. 通信技术,2022,55(10):1376-1382.

[2] 耿文凤. 基于FPGA的光纤信息安全传输系统设计[J]. 激光杂志,2021,42(8):115-119.

[3] 尹震宇,许鹏,徐福龙. 基于FPGA SoC的EtherCAT协议栈设计与实现[J]. 小型微型计算机系统,2022,43(8):1751-1755.

[4] 吴云军,温玉屏,纪巍,等. 基于FPGA的安全策略搜索设计与实现[J]. 舰船电子工程,2022,42(7):116-120.

[5] 魏晓艳. 基于FPGA的千兆以太网数据通信接口设计与实现[J]. 微型电脑应用,2022,38(5):69-72.

京公网安备 11011302003690号

京公网安备 11011302003690号