- 收藏

- 加入书签

基于FPGA的总线测试系统

摘要:本文介绍了基于FPGA的1553B总线测试系统的设计与实现。该系统包括1553B总线测试卡硬件电路设计和控制软件设计两部分。硬件电路设计中,描述了FPGA与BU-61580(1)接口、FPGA与BU-61580(2)接口以及FPGA与USB接口的设计。在控制软件设计方面,包括USB接口程序设计、BU-61580配置模块设计和总线测试模块设计。最后,对系统进行了测试验证,证明了其性能和可靠性。

关键词:FPGA;1553B总线;测试系统

引言:MIL-STD-1553B总线是一项军用串行总线标准,提供了高度可靠的总线通信协议,广泛应用于航空电子、卫星导航、武器系统等领域。中国早在20世纪90年代就开始研究和开发1553B协议,并将其纳入军事标准GJB289A《数字式时分制指令/响应型多路传输数据总线》。目前,机载、弹载、舰载和车载系统均将1553B总线视为核心组成部分,需求量逐年增加。

1.1553B总线测试系统总体设计

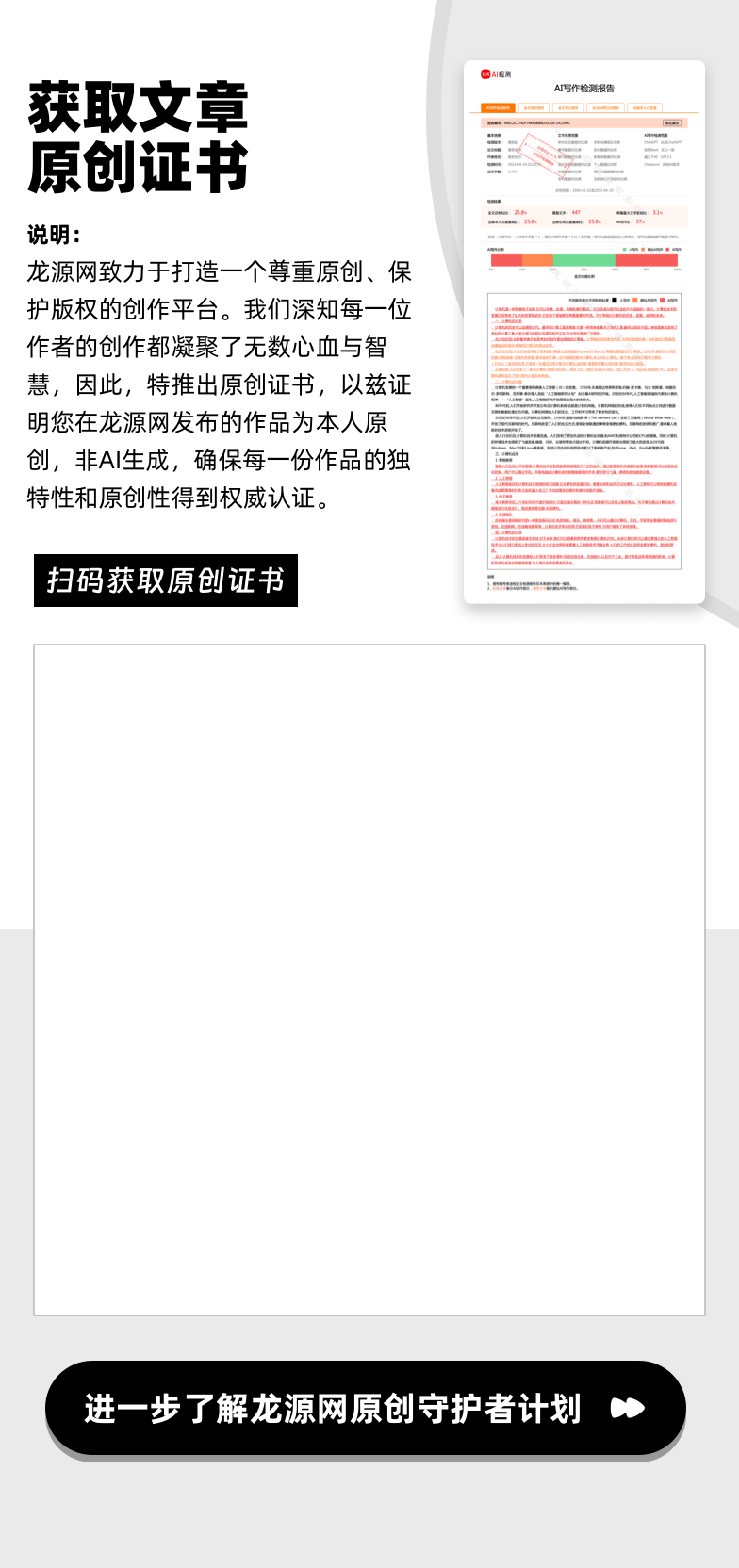

本次设计的1553B总线测试系统旨在满足1553B总线测试的复杂性和实时性要求,使用户能够根据测试需求快速搭建系统。系统架构包括上位机软件、1553B总线测试卡和被测1553B总线设备。上位机软件分为驱动层、接口层和应用层,负责系统与用户的交互。硬件层包括USB接口单片机CY7C68013、主控FPGA(XC3S400)以及两片BU-61580。驱动层的驱动程序与USB接口单片机的固件程序协作,实现上位机与测试卡之间的命令和数据传递。接口层封装了与测试卡的通信接口,应用层则负责测试流程和逻辑的实现。主控FPGA响应应用软件的控制命令,初始化配置BU-61580,发起总线数据传输,监控总线数据,并模拟RT响应BC,将监控数据和各种数据请求上传至上位机。用户根据测试需求配置BU-61580,通过应用软件发送命令和测试数据至主控FPGA,完成测试流程。这个系统通过数据环路实现了1553B总线测试,提供了灵活、可定制的解决方案,以满足不断增长的测试需求[1]。详情如图1所示。

2.1553B总线测试卡硬件电路设计

2.1FPGA与BU-61580(1)接口设计

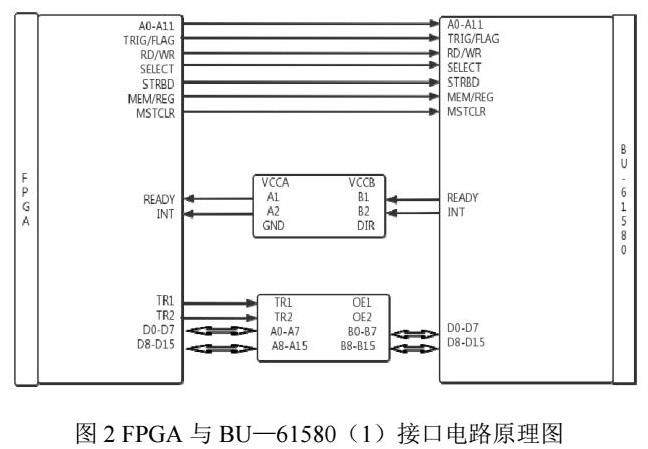

FPGA与BU-61580(1)接口设计是为了实现1553B总线测试系统中BC(Bus Controller)与FPGA之间的通信和数据传输。BC负责模拟总线控制,而FPGA需要与BC协同工作以完成数据交换和控制命令的传递。在设计中,考虑到FPGA的电平接口为3.3V,而BU-61580(1)的电平接口为5.3V,因此采用了3.3V和5V之间的电平转换。为了实现数据总线通信,使用了SN74ALVC164245-EP芯片,这是一个16位的3.3V至5V电平转换收发芯片。将FPGA的A端与SN74ALVC164245-EP的A端连接,将BU-61580(1)的数据总线与SN74ALVC164245-EP的B端连接,从而实现数据的双向传输。控制方向通过FPGA来实现,通过控制OE1、OE2、TR1和TR2信号的状态,可以控制数据是由A到B还是由B到A传输。此外,BU-61580(1)有17个寄存器和4K×16位的存储空间,所以需要12位地址总线(A0~A11)和16位数据总线(A0~A15)来进行通信。地址总线和控制信号的方向是单向的,无需进行电平转换,而数据总线是双向的,需要进行电平转换。为了反馈信息给FPGA,需要将READY信号和INT信号传递回FPGA。这些信号需要经过电平转换,使用了SN74LVC2T45等类似的电平转换芯片。此外,方向控制DTROE1和DTROE2由BU-61580控制,从B到A的方向。详情如图2所示。

2.2FPGA与BU-61580(2)接口设计

FPGA与BU-61580(2)接口设计是为了实现1553B总线测试系统中BM(Bus Monitor)/RT(Remote Terminal)与FPGA之间的通信和数据传输。BU-61580(2)在BM和RT共同工作模式下,其内部存储空间已经无法满足BM和RT配置表及消息块的存储需求,因此需要扩展外部RAM作为存储空间。在FPGA中预留了12KB×16位的FIFO作为BU-61580在RT模式下的外部RAM,用于统一存储BM和RT的配置表和消息块,并方便接收和上传BM的监测数据。

在BM/RT模式下,BU-61580访问FPGA中FIFO的信号方向是从BU-61580到FPGA,因此需要考虑地址总线的电平匹配。为了实现电平匹配,使用了电平转换芯片。这些转换芯片确保了信号的正常传输,尤其是地址总线的匹配。在RT模式下,RT地址需要由FPGA来控制,因此需要增加RT地址线(RTA0~RTA4)以及相关控制信号。相比于BC模式,RT模式下的控制信号有所增加,以满足RT模式下的需求。

2.3 FPGA与USB接口设计

FPGA与USB接口的设计涉及到Cypress公司生产的USB2.0控制器CY7C68013,其提供了一种独特的接口方式,即通用可编程接口(GPIF)方式。在GPIF方式的设计中,GPIF充当CY7C68013的端点FIFO的内部控制器,允许数据传输时CPU无需干涉。接口的电路中FD0~FD15表示GPIF数据总线,USB主机通过CY7C68013与外部设备进行数据传输,可以选择8位或16位数据传输。CTL0~CTL是GPIF的输出控制信号,CY7C68013用于控制外部设备。RDY0~RDY2是GPIF的输入信号,CY7C68013用于检测外部设备的状态。PA0~PA7是GPIF提供给外部设备的地址线。这种设计确保了FPGA与USB控制器之间的数据传输和控制信号的有效连接,为系统提供了高效的数据传输通道,使USB接口可以在1553B总线测试系统中无干扰地进行数据传输。

3.1553B总线测试卡控制软件设计

3.1USB接口程序设计

USB接口程序设计包括驱动层和接口层,用于实现上位机与硬件层之间的命令发送、状态获取和数据传输。这部分程序的目标是为用户提供一个标准的接口,以方便控制和通信。在驱动层,使用Cypress公司的EZ-USB FX2开发包中包含的驱动程序,并进行必要的修改。主要修改包括DeviceIoControl例程,以增加对数据传输的控制。这部分包括命令和数据的发送与接收函数,这些函数在上层应用软件与底层驱动程序之间充当接口层的角色。这些函数用于设备控制命令,如启动设备、停止设备和复位设备等,同时提供标准的命令发送和数据收发接口函数。接口函数在Visual C++6.0中使用Cypress公司提供的库函数来实现,并最终以动态链接库的形式提供给用户。这样,用户可以轻松地控制设备并进行数据传输,从而实现与1553B总线测试系统的通信和控制[2]。

3.2应用软件设计

3.2.1BU—61580配置模块设计

BU-61580配置模块的设计是系统中的标准部分,其配置功能和方法对于各种测试流程都是通用的。因为系统中使用了两块BU-61580分别作为BC(Bus Controller)和BM/RT(Bus Monitor/Remote Terminal),所以配置软件需要分别对BU-61580(1)和BU-61580(2)进行配置。配置软件的总体设计方法是在应用软件中实现BU-61580用户手册提供的配置项,由用户进行具体配置。配置模块会将用户输入的配置参数按照特定的配置命令帧格式生成配置数据文件。在这个过程中,应用软件会对用户输入的配置参数进行合法性检验,确保配置参数的有效性。一旦检验通过,配置数据文件将通过USB接口发送至FPGA,然后由FPGA对数据进行校验和解析,最终将配置值写入相应的存储空间。对于BC和BM/RT的配置,主要区别在于配置项的写入位置,BC模式配置项写入BU-61580(1)芯片的4KB RAM空间,而BM/RT模式配置项写入BU-61580(2)芯片的4KB RAM空间。RT的数据则被写入FPGA内部的8KB FIFO存储空间。

配置软件在发送配置参数时,按照一定的帧长度(每次读取16字节,即一个配置帧长度的数据)的方式进行数据发送。配置软件会调用命令发送函数SendCmd,将一个2字节的参数配置命令0xFAFB发送给主控FPGA。主控FPGA收到该命令后,会等待接收参数配置帧。配置软件立刻调用命令发送函数SendCmd,将一个长度为16字节的参数配置帧发送给主控FPGA。主控FPGA接收到参数配置帧后,会对帧数据进行校验,确保数据的完整性。如果校验通过,主控FPGA会按照参数配置帧的格式解析其中的地址信息和参数值,并将配置参数写入到指定的配置地址中。完成配置后,主控FPGA会上传一个操作成功的回令0xFA01。如果数据校验失败,或者在指定的时间内主控FPGA没有接收到参数配置帧,主控FPGA会上传一个操作失败的回令0xFA00。在配置软件发送完一个参数配置帧后,其会调用接收回令函数GetCmd,以接收主控FPGA的返回回令。根据回令的值,如果是0xFA01,则配置软件继续读取配置文件中的下一个参数配置帧并发送。如果回令是0xFA00,则配置软件将重新发送当前的参数配置帧。

3.2.2总线测试模块设计

为了实现1553B总线的自动测试并满足测试过程中的实时性要求,测试过程和测试用应答消息的内容是通过软件总线测试模块进行配置的。配置的消息会按照特定的帧格式进行组帧,然后批量发送给主控FPGA,主控FPGA会根据1553B总线节点的通信过程自动应答这些消息。在实际的测试过程中,用户需要根据1553B总线上的数据/命令发送传输方向和时间间隔,逐个配置每个消息。总线测试模块的软件会根据用户输入的信息按照特定的消息配置命令帧格式进行组帧,生成总线测试命令控制文件。然后,通过USB接口将总线测试命令控制文件发送给主控FPGA,主控FPGA会根据控制文件中的内容自动完成1553B总线消息的发送和接收[3]。

总线测试命令控制文件的下发过程按照特定的命令格式进行发送。上位机软件会调用命令发送函数SendCmd,将控制命令"0xCC01"发送给主控FPGA。然后,上位机软件会调用接收回令函数GetCmd,以接收主控FPGA的返回回令。如果回令的值是"0xCC02",则上位机软件会根据特定格式组织数据包,调用WriteBulk函数来发送文件内容。如果回令值不是"0xCC02"或者超时未接收到回令值,上位机软件会重新发送控制命令"0xCC01"。这个过程会一直重复,直到整个总线测试命令控制文件的下发完成。对于最后一个文件数据包,如果不足126字节,将会被全部填充为0,以确保每个文件数据包的长度都是一致的。

4.测试验证

在测试验证过程中,DTREQ是BU-61580向FPGA发送的接口总线请求信号,当其处于低电平时表示BU-61580请求访问FPGA。DTACK是FPGA的接口总线请求响应信号,如果其处于低电平,表示FPGA正在响应接口总线请求。DTREQ有效后的500 ns内,DTACK也有效,且其几乎同时升高,与芯片资料中的时序要求相符。MEMOE用于使能外部RAM数据的输出,相当于读外部RAM信号,而在这个设计中,外部RAM就是FPGA的内部FIFO。MEMWR是写RAM信号,当其处于低电平时有效。在DTREQ请求信号有效后,MEMOE执行了5次读取外部RAM数据,依次读出堆栈地址、消息时间间隔字、消息块地址、BC控制字和BC状态字。然后,MEMWR有效两次,将定时标签字和BC块状态字写入相应的地址。所有这些时序操作都与BU-61580芯片资料中所介绍的时序关系相匹配。因此,通过总线测试软件成功地控制了BU-61580,实现了1553B总线测试系统的快速定制,验证了系统的正常工作[4]。

总结:

在基于FPGA的1553B总线测试系统的开发中成功地应对了军事和航空领域的需求,为1553B总线设备的测试和验证提供了强大的工具。这一系统整合了硬件电路设计和控制软件开发,以实现高可靠性和高度定制化的测试解决方案。这种技术将继续为军事、航空电子和其他相关领域的工程师提供支持,以确保系统的可靠性和性能。随着需求的不断增加,这一领域的发展前景非常广阔。

参考文献:

[1]韦佳霄,王健.基于PCI总线的燃气舵机测试系统实现[J].电子制作,2023,31(12):114-116+120.

[2]宋云霞,刘永涛,黄田韵.基于CPCI总线技术的相控阵天线测试系统设计[J].火控雷达技术,2023,52(01):115-118+124.

[3]孙骜,秦旭军.基于FPGA的多通道ARINC429总线测试系统[J].电子技术应用,2023,49(01):119-123.

[4]刘四海,吴可,孙丹峰等.基于PCIE总线的双框架控制力矩陀螺控制器串行/并行自动测试系统设计与实现[J].制造业自动化,2022,44(05):38-42.

京公网安备 11011302003690号

京公网安备 11011302003690号